CMOSデジタル回路

CMOSデジタル回路を設計するためのメモ。

nMOSトランジスタとpMOSトランジスタ

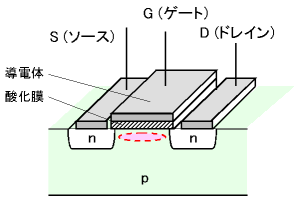

下図はnMOSトランジスタを模式的に表したものである。

ゲート部はMetal(導電体)- Oxide(酸化膜)- Semiconductor(半導体) という構造をとっており,この頭文字をとってMOSと呼ばれる。

通常の状態ではソース-ドレイン間に電流は流れないが、ゲートにある閾値以上の正電圧を加えた場合、ゲート直下のp型領域に電子が集まり、キャリアの通り道(チャネル)が形成され、ソース-ドレイン間に電流が流れる。

ここで,上図のようにn型のチャネル(多数キャリア:電子)が形成されるMOSトランジスタを「nMOSトランジスタ」、逆にp型のチャネル(多数キャリア:正孔)が形成されるMOSトランジスタを「pMOSトランジスタ」という。

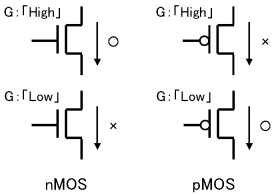

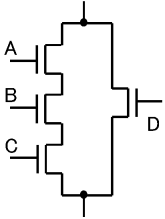

下図はnMOSとpMOSの、デジタル回路における性質を表したものである。

デジタル回路では、nMOSは「ゲートにHを加えると閉じるスイッチ」、pMOSは「ゲートにLを加えると閉じるスイッチ」と考えることができる。

CMOS回路

ソース-ドレイン間導電性の特徴は、nMOSトランジスタとpMOSトランジスタで大きく異なる。特性の記述はここでは省くが、デジタル回路においてnMOSトランジスタは

- Hが正確に伝わらない

- Lは正確に伝わる

という特徴を持ち、pMOSトランジスタは

- Hは正確に伝わる

- Lが正確に伝わらない

と、正反対の特徴を持つ。この2つの特徴を踏まえ、HとLを両方とも正確に伝えるため、それぞれの欠点を補い合うように構成した回路をCMOS(Complementary MOS)回路と呼ぶ。

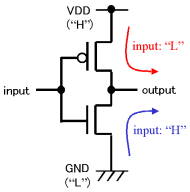

例として、CMOS回路で構成したインバータ(NOT)回路を下図に示す。

この回路は、inputがHのときにはnMOSを通してoutputがLとなり、inputがLのときにはpMOSを通してoutputがHとなる。つまり、各々のMOSトランジスタでは自分の得意な信号のみを伝えている。

CMOS組合わせ回路の設計

次に、論理式を元にしてCMOS回路を設計する方法を示す。CMOS回路は一般に以下のような手順で構成することができる。

- 論理を反転する

- nMOS回路を作る

- pMOS回路を作る

- nMOS回路とpMOS回路を接続する

ここでは例として、以下のような論理式に対応するCMOS回路を設計する。

1. 論理の反転

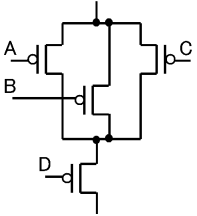

2. nMOS回路

反転した論理式に対し、

- 論理積→直列

- 論理和→並列

というルールに従い、nMOSトランジスタを並べる。

3. pMOS回路

反転した論理式に対し、

- 論理積→並列

- 論理和→直列

というルール(nMOSの逆)に従い、pMOSトランジスタを並べる。

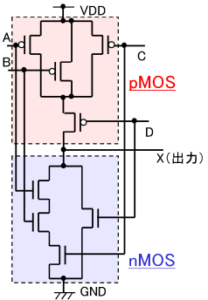

4. nMOSとpMOSの接続

上から

- VDD

- pMOS回路

- nMOS回路

- GND

の順に接続し、pMOSとnMOSの間から出力を出す。

ディスカッション

コメント一覧

まだ、コメントがありません